# CAN1630G SPDT Switch Datasheet

Rev 1.2 April, 2019

This datasheet is intended for customer's evaluation and application of the CAN1630G device. Under no circumstances it should be circulated outside the customer's company. This datasheet is preliminary and CanaanTek reserves the right to modify and to improve the data.

### PRODUCT DESCRIPTION

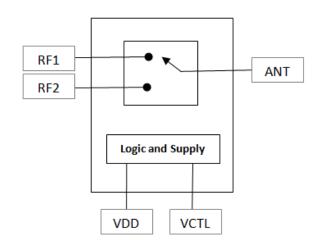

CAN1630G is a single pole, dual-throw (SPDT) LTE MMMB transmit/receive switch. Switching is controlled by an integrated GPIO interface with a single control pin. Depending on the logic voltage level applied to the logic control pin, the antenna port is connected to one of the switched RF ports (RF1 or RF2) through a low insertion loss path, while the path between the antenna port and the other RF port is in a high isolation high impedance state.

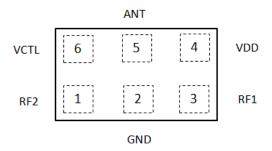

No external DC blocking capacitors are required as long as no DC voltage is applied on any RF path. The CAN1630G is manufactured using a state-of-the-art Silicon-On-Insulator (SOI) process and is provided in a compact 1.1 x 0.7 x 0.45 mm, 6-pin surface mount Dual Flat No-Lead (DFN) package. A functional block diagram is shown in Figure 1. The pin configuration and package are shown in Figure 2. Signal pin assignments and functional pin descriptions are provided in Table 1.

# **FEATURES**

- Broadband frequency range: 0.1 to 2.7 GHz

- Single GPIO control line with VDD voltage regulator:

- V<sub>CTL</sub> = 1.8 V typical

- $V_{DD} = 2.85V$  typical

- Small, DFN (6-pin, 1.1 x 0.7 x 0.45 mm) package (MSL1, 260 °C per JEDEC J-STD-020)

### **APPLICATIONS**

- 3G and 4G LTE TDD/FDD transmit/receive

- Embedded modules

Figure 1. CAN1630G Block Diagram

(Top View)

Figure 2. CAN1630G Pinout

**Table 1. CAN1630G Signal Descriptions**

| Pin# | Name | Description     | Pin# | Name              | Description         |

|------|------|-----------------|------|-------------------|---------------------|

| 1    | RF2  | RF I/O, throw 2 | 4    | VDD               | Voltage supply      |

| 2    | GND  | Ground          | 5    | ANT               | RF I/O, switch pole |

| 3    | RF1  | RF I/O, throw 1 | 6    | VCTL <sup>1</sup> | Switch control line |

Note 1: If VDD is powered down, VCTL should be low level.

### **Electrical and Mechanical Specifications**

The absolute maximum ratings of the CAN1630G are provided in Table 2.

Electrical specifications are provided in Table 3.

The state of the CAN1630G is determined by the logic provided in Table 4.

Table 2. CAN1630G Absolute Maximum Ratings

| Parameter               | Symbol           | Minimum | Maximum | Unit      |

|-------------------------|------------------|---------|---------|-----------|

| Supply voltage          | VDD              | 1.6     | 5.0     | V         |

| Digital control voltage | VCTL             | 0.0     | 3.3     | V         |

| RF input power          | Pin              |         | 35      | dBm       |

| Supply ripple           | $V_{PP}$         |         | 20      | $mV_{PP}$ |

| Operating temperature   | Тор              | -40     | +85     | °C        |

| Storage temperature     | T <sub>STG</sub> | -55     | +150    | °C        |

Note: Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.

**CAUTION:** Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times.

# Table 3. CAN1630G Electrical Specifications (Note 1)

$(V_{DD} = 2.85V, T_{OP} = +27$  °C, Characteristic Impedance [Z<sub>O</sub>] = 50  $\Omega$ , Unless Otherwise Specified)

| Parameter                                        | Symbol | Test Condition                                                                                                                 | Min            | Typical              | Max                  | Units          |

|--------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|----------------------|----------------|

| DC Specifications                                |        |                                                                                                                                |                |                      |                      |                |

| Supply voltage                                   | VDD    |                                                                                                                                | 1.60           | 2.85                 | 4.5                  | V              |

| Control voltage:                                 |        |                                                                                                                                |                |                      |                      |                |

| Low                                              | VCTL_L |                                                                                                                                | 0              | 0                    | 0.40                 | V              |

| High                                             | VCTL_H |                                                                                                                                | 1.20           | 1.80                 | VDD                  | V              |

| Current on VCTL pin                              | I_CTL  |                                                                                                                                |                |                      | 5                    | μΑ             |

| Supply current                                   | IDD    | VDD = 2.85 V, VCTL = VCTL_H                                                                                                    |                | 35                   | 60                   | μΑ             |

| RF path switching time                           | tSW    | Measured from VCTL_HIGH minimum or VCTL_LOW maximum to RF output power ± 1 dB (Note 2), PIN = +26 dBm, Top = -10 °C to +85 °C. |                | 1                    | 3                    | μs             |

| RF Specifications                                |        |                                                                                                                                |                |                      |                      |                |

| Insertion loss (RF1 or RF2 to ANT pin)           | IL     | 0.1 to 1.0 GHz<br>1.0 to 2.2 GHz<br>2.2 to 2.7 GHz                                                                             |                | 0.30<br>0.35<br>0.37 | 0.50<br>0.55<br>0.60 | dB<br>dB<br>dB |

| Isolation from any active port to any other port | Iso    | 0.1 to 1.0 GHz<br>1.0 to 2.2 GHz<br>2.2 to 2.7 GHz                                                                             | 30<br>28<br>20 | 35<br>33<br>25       |                      | dB<br>dB<br>dB |

| 0.1 dB Input Compression Point                   | P0.1dB | VDD=2.85V                                                                                                                      |                | 34.5                 |                      | dBm            |

| Voltage Standing Wave<br>Ratio, all ports        | VSWR   | Referenced to 50 Ω,0.1 to 2.7 GHz                                                                                              |                | 1.2:1                | 1.5:1                | -              |

| Harmonic RF1 or RF2 to                           | Harm   | fo = 0.1 to 2.7 GHz,<br>PIN = +26 dBm,<br>VSWR = 2.5:1                                                                         |                | -65                  | -55                  | dBm            |

Note 1: Performance is guaranteed only under the conditions listed in this Table.

Note 2: RF output power is defined as PIN (dBm) - IL (dB).

**Table 4. CAN1630G Truth Table**

| State | Active Path | VCTL (Pin 6) |

|-------|-------------|--------------|

| 0     | ANT to RF1  | 0            |

| 1     | ANT to RF2  | 1            |

**Note:** "1" = 1.20 V to VDD. "0" = 0.0 V to 0.40 V.

### **Evaluation Board Description**

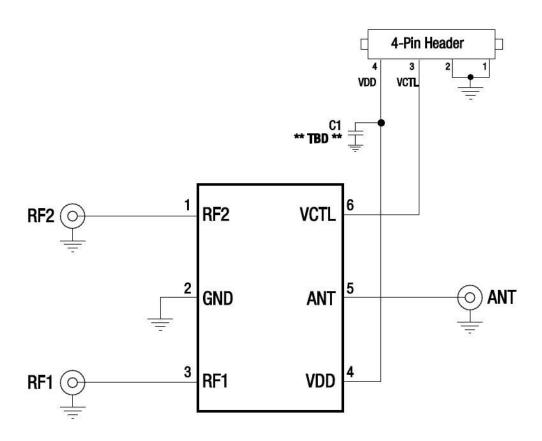

The CAN1630G Evaluation Board is used to test the performance of the CAN1630G SPDT Switch. An Evaluation Board schematic diagram is provided in Figure 3.

Figure 3. CAN1630G Evaluation Board Schematic

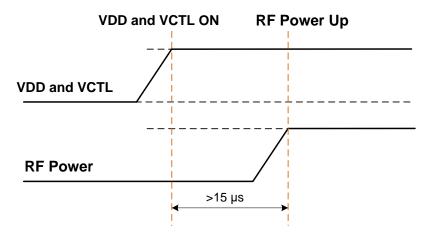

### **Timing Requirements**

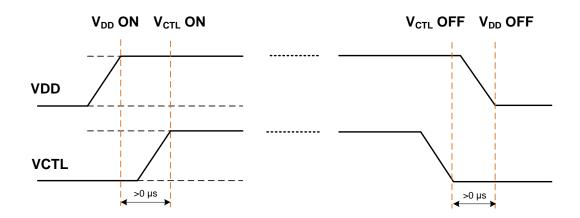

It is important that the user adheres to the correct timing sequences in order to avoid leakage power consumption.

VDD and VCTL cannot be powered on and off independently from one another. During power on sequence, the user must power up VDD first, then power up VCTL. During power off sequence, the user must power off VCTL first, then power off VDD. In the state of VDD=OFF(0 V) and VCTL=ON(1.8V), it may cause leakage power consumption as ESD protection circuit inside the switch.

Figure 4. Allowable Power On Sequences

2. VDD and VCTL must be on for a minimum of 15us before applying RF power.

Figure 5. RF Power-Up Detail

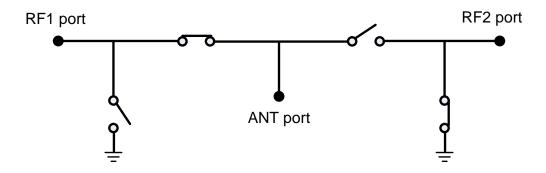

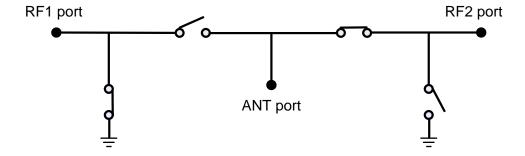

### Switch Model for RF ON/OFF state

Please note that Switch model for RF1 ON and RF2 ON as the following.

Refer to the Figure 6, when RF1 ON, RF1 port and ANT port will be connected directly in short circuit, while RF2 port will be connected to the Ground through internal switch, so it should avoid DC level applied on RF2 port.

Refer to the Figure 7, it's vise versa for RF2 ON.

Figure 6. Switch model with RF1 ON

Figure 7. Switch model with RF2 ON

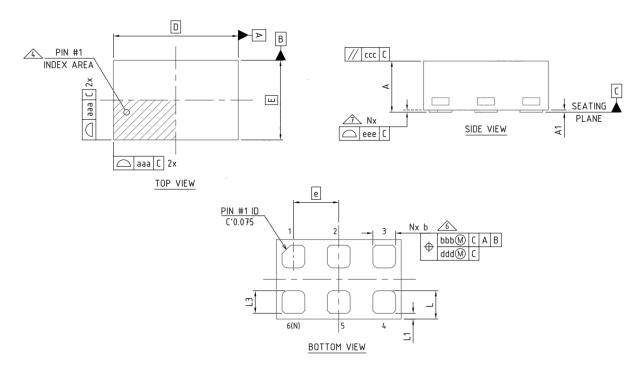

## **Package Dimensions**

Package dimensions for the CAN1630G are shown in Figure 5.

|        | MILLMETER |      |      |  |

|--------|-----------|------|------|--|

| SYMBOL | MIN       | NOR  | MAX  |  |

| А      | 0.41      | 0.45 | 0.50 |  |

| A1     | 0.00      | 0.02 | 0.05 |  |

| b      | 0.15      | 0.20 | 0.25 |  |

| D      | 1.10 BSC  |      |      |  |

| E      | 0.70 BSC  |      |      |  |

| е      | 0.40 BSC  |      |      |  |

| L      | 0.15      | 0.25 | 0.35 |  |

| L1     | 0.00      | 0.05 | 0.10 |  |

| L3     | 0.15      | 0.20 | 0.25 |  |

| aaa    | 0.05      |      |      |  |

| bbb    | 0.07      |      |      |  |

| ccc    | ccc 0.10  |      |      |  |

| ddd    | 0.05      |      |      |  |

| eee    |           | 0.08 |      |  |

Figure 8. CAN1630G Package Dimensions

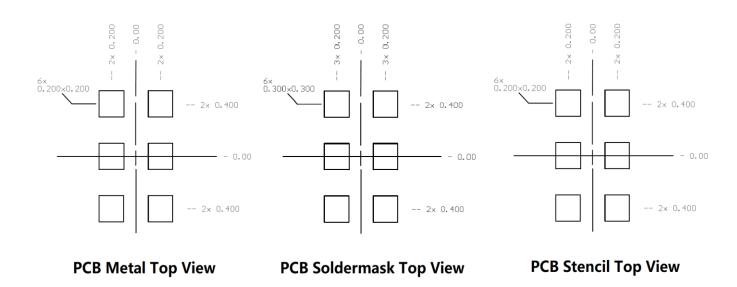

### PCB Metal, Solder, and Stencil Patterns

Figure 9. CAN1630G PCB Metal, Solder, and Stencil Patterns

### **Package and Handling Information**

Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

THE CAN1630G is rated to Moisture Sensitivity Level 1 (MSL1) at 260 °C. It can be used for lead or lead-free soldering.

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

# **Revision History**

| Revision | Comments                                                             |  |  |

|----------|----------------------------------------------------------------------|--|--|

| Rev1.0   | First Draft                                                          |  |  |

| Rev 1.1  | Add PCB Metal, Solder, and Stencil Patterns                          |  |  |

| Rev 1.2  | Add timing requirement, RF ON/OFF model description and Typo correct |  |  |

|          |                                                                      |  |  |

|          |                                                                      |  |  |

|          |                                                                      |  |  |

|          |                                                                      |  |  |

|          |                                                                      |  |  |